Gifting Made Simple

Give the Gift of ChoiceClick below to purchase a Bramalea City Centre eGift Card that can be used at participating retailers at Bramalea City Centre.Purchase HereHome

Fault-Tolerance Techniques for SRAM-based FPGAs by Fernanda Lima Kastensmidt, Hardcover | Indigo Chapters

Coles

Loading Inventory...

Fault-Tolerance Techniques for SRAM-based FPGAs by Fernanda Lima Kastensmidt, Hardcover | Indigo Chapters in Brampton, ON

By Fernanda Lima Kastensmidt

Current price: $160.95

Coles

Fault-Tolerance Techniques for SRAM-based FPGAs by Fernanda Lima Kastensmidt, Hardcover | Indigo Chapters in Brampton, ON

By Fernanda Lima Kastensmidt

Current price: $160.95

Loading Inventory...

Size: 1 x 11.69 x 1.71

*Product information may vary - to confirm product availability, pricing, and additional information please contact Coles

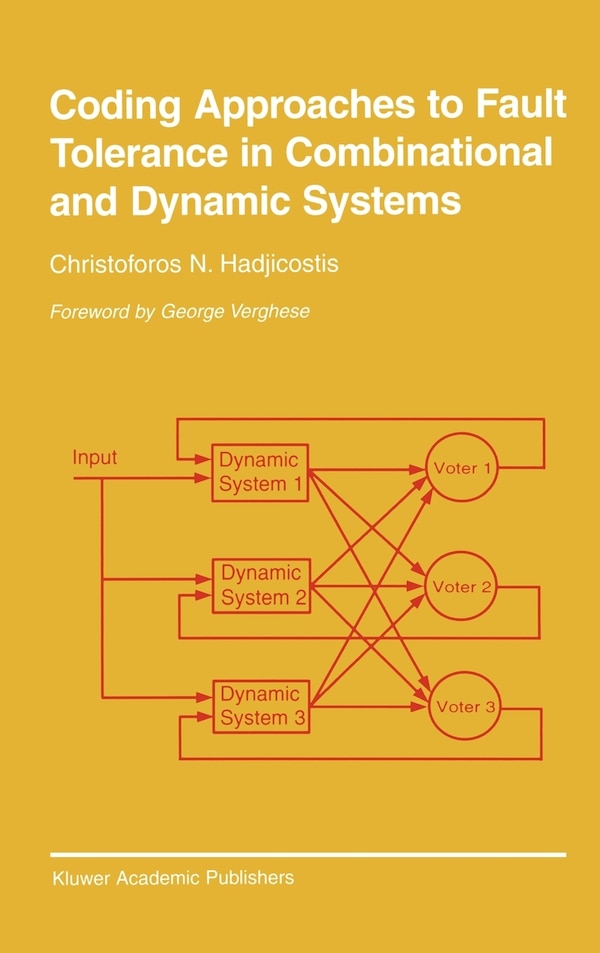

Fault-tolerance in integrated circuits is not an exclusive concern regarding space designers or highly-reliable application engineers. Rather, designers of next generation products must cope with reduced margin noises due to technological advances. The continuous evolution of the fabrication technology process of semiconductor components, in terms of transistor geometry shrinking, power supply, speed, and logic density, has significantly reduced the reliability of very deep submicron integrated circuits, in face of the various internal and external sources of noise. The very popular Field Programmable Gate Arrays, customizable by SRAM cells, are a consequence of the integrated circuit evolution with millions of memory cells to implement the logic, embedded memories, routing, and more recently with embedded microprocessors cores. These re-programmable systems-on-chip platforms must be fault-tolerant to cope with present days requirements. This book discusses fault-tolerance techniques for SRAM-based Field Programmable Gate Arrays (FPGAs). It starts by showing the model of the problem and the upset effects in the programmable architecture. In the sequence, it shows the main fault tolerance techniques used nowadays to protect integrated circuits against errors. A large set of methods for designing fault tolerance systems in SRAM-based FPGAs is described. Some presented techniques are based on developing a new fault-tolerant architecture with new robustness FPGA elements. Other techniques are based on protecting the high-level hardware description before the synthesis in the FPGA. The reader has the flexibility of choosing the most suitable fault-tolerance technique for its project and to compare a set of fault tolerant techniques for programmable logic applications. | Fault-Tolerance Techniques for SRAM-based FPGAs by Fernanda Lima Kastensmidt, Hardcover | Indigo Chapters

Fault-tolerance in integrated circuits is not an exclusive concern regarding space designers or highly-reliable application engineers. Rather, designers of next generation products must cope with reduced margin noises due to technological advances. The continuous evolution of the fabrication technology process of semiconductor components, in terms of transistor geometry shrinking, power supply, speed, and logic density, has significantly reduced the reliability of very deep submicron integrated circuits, in face of the various internal and external sources of noise. The very popular Field Programmable Gate Arrays, customizable by SRAM cells, are a consequence of the integrated circuit evolution with millions of memory cells to implement the logic, embedded memories, routing, and more recently with embedded microprocessors cores. These re-programmable systems-on-chip platforms must be fault-tolerant to cope with present days requirements. This book discusses fault-tolerance techniques for SRAM-based Field Programmable Gate Arrays (FPGAs). It starts by showing the model of the problem and the upset effects in the programmable architecture. In the sequence, it shows the main fault tolerance techniques used nowadays to protect integrated circuits against errors. A large set of methods for designing fault tolerance systems in SRAM-based FPGAs is described. Some presented techniques are based on developing a new fault-tolerant architecture with new robustness FPGA elements. Other techniques are based on protecting the high-level hardware description before the synthesis in the FPGA. The reader has the flexibility of choosing the most suitable fault-tolerance technique for its project and to compare a set of fault tolerant techniques for programmable logic applications. | Fault-Tolerance Techniques for SRAM-based FPGAs by Fernanda Lima Kastensmidt, Hardcover | Indigo Chapters